-

5nm FinFET Accredited Service LaboratoryFIB Circuit Edit ServiceADVANCED CIRCUIT ENGINEERS, LLC.

5nm FinFET Accredited Service LaboratoryFIB Circuit Edit ServiceADVANCED CIRCUIT ENGINEERS, LLC.

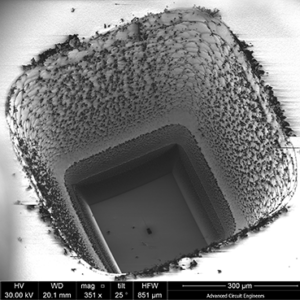

FIB Circuit Edit

ADVANCED FIB CIRCUIT EDIT

Front and Backside FIB Circuit modification services | Backside Sample Preparation

ACE offers both Frontside and full-thickness Backside FIB Circuit Editing down to 5nm process tech-nodes.

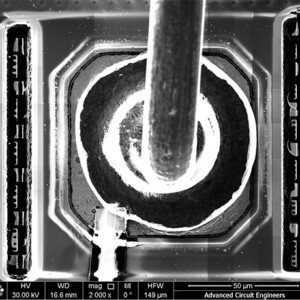

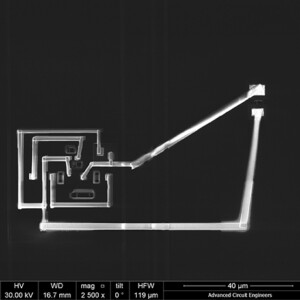

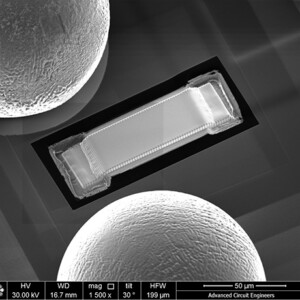

FIB Circuit Edit offers quick-fix IC debug verification of design changes within initial flawed silicon runs. FIB modifications allow for disconnecting of IC metal traces, multiple jumper connections, post packaged flip-chip “backside fib circuit edit” as well as probe-pad node access deposition for electrical testing. Utilizing advanced proprietary techniques, we are able to perform IC modifications down to 5nm.

RESULTS

- Proven 5nm FIB circuit edit success.

- Full thickness FIB Backside edit (no sample prep required)

- Front & Backside FIB circuit edits.

- 12″ full wafer FIB edit.

- FIB nano-machining

COMPETITIVELY PRICED

- Discounts for volume work.

- No “rush-surcharge” expedite fees and free weekend work.

- Quick turn-around.

- Free local delivery and pickup services

Free consultation

- Free layout FIB design.

- Our engineers will work with you and your team on implementing the highest FIB yield design to achieve your circuit edit goals.

CAPABILITIES AND INFORMATION

ADVANCED CAPABILITIES

5nm FinFET, 14/16nm FinFET, 28nm: Front & Backside FIB circuit edits.

STANDARD CAPABILITIES

40nm, 45nm, 65nm, .13um, .18um, .25um, .35um: Front & Backside FIB circuit modification.

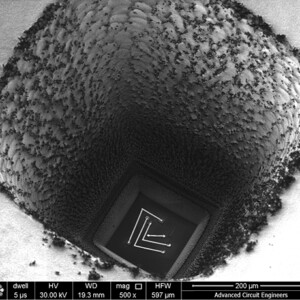

FULL THICKNESS BACKSIDE FIB EDIT

No sample preparation required. Maintains silicon integrity / thermal properties.

EXPERIENCE / YIELD

Over 50-years experience (+ 50,000 hours) techniques and innovative FIB circuit edit expertise.

PACKAGE TYPE

BGA, QFN, CSP, WLBGA, 8″ wafer, packaged “flip-chip”, die level

WAFER SIZE ACCOMMODATIONS

- 4″, 6″, 8″ and 12″ wafer.

- 300mm (12″ full-wafer) FIB Circuit edit

BACKSIDE SAMPLE PREPARATION

Mechanical polish of bulk SI down to ~100um for flip-chip “backside” editing.